## **Chapter 6: Registers and Counters**

- 6.1 Registers

- 6.2 Shift Registers

- 6.3 Ripple Counters

- 6.4 Synchronous Counters

- 6.5 Other Counters

## **6.1 Registers**

- A *register* is a group of FFs, each FF shares a common clock and is capable of storing one bit of information.

- An *n*-bit register consists of a group of *n* FFs capable of storing *n* bits of binary information.

- A register may have combinational gates that perform certain data-processing tasks.

- The simplest register is contains only FFs.

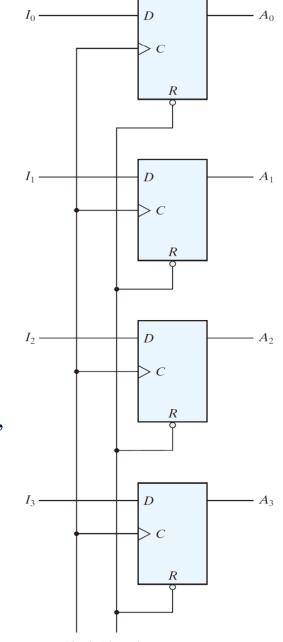

- Example: four *D*-FFs form a 4-bit data storage register.

- The clock positive edge triggers all FFs, and the binary data at the four inputs are transferred into the register.

- (*I*<sub>3</sub>, *I*<sub>2</sub>, *I*<sub>1</sub>, *I*<sub>0</sub>) determines (*A*<sub>3</sub>, *A*<sub>2</sub>, *A*<sub>1</sub>, *A*<sub>0</sub>) at the clock edge, and the four outputs can be sampled at any time.

- *Clear\_b* is active-low to reset FFs asynchronously.

- The *R* inputs must be maintained at logic 1 (i.e., de-asserted) during normal clocked operation.

Clock Clear\_b

## **4-bit Register with Parallel Load**

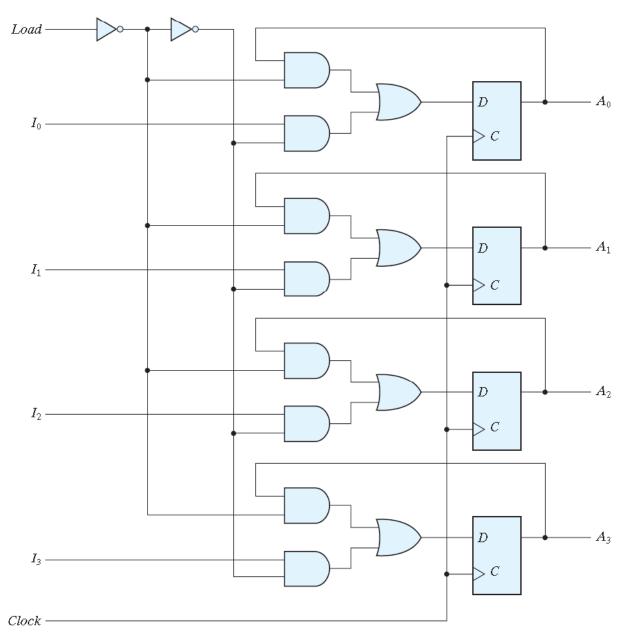

- The transfer of new information into a register is referred to as *loading* or *updating*.

- If all the bits of the register are loaded simultaneously with a common clock pulse, it is called as *parallel* loading.

- Two-channel mux selects either the data bus or the output of the register to the register.

- *Load* is for the selection of mux's.

## **6-2 Shift Registers**

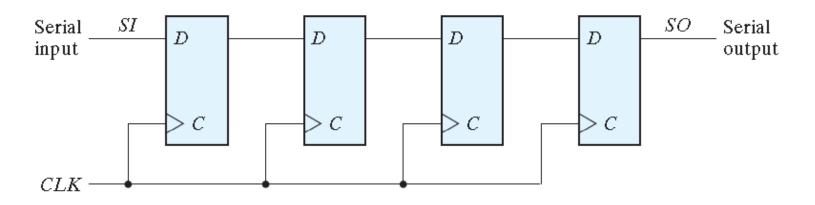

- *Shift register* is a cascaded chain of FFs with the output of each FF connected to the input of the next FF.

- It is capable of shifting the binary information held in each FF to its neighboring FF, in a selected direction.

- All FFs receive common clock to activate the shift of data.

- The simplest possible shift register uses only FFs, as shown below.

- This shift register is unidirectional (left-to-right).

- The serial input determines what goes into the leftmost FF during the shift.

- The *serial output* is taken from the output of the rightmost FF.

# **Serial Transfer**

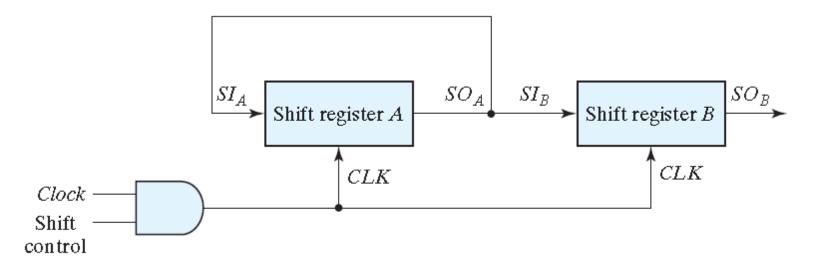

- Serial mode: information is transferred and manipulated one bit at a time by shifting the bits out of the source register and into the destination register.

- Serial transfer is done with shift registers, as shown below.

• Rotation: circulating connection of register A prevent the loss of information.

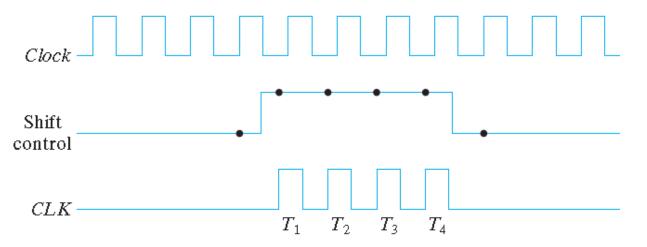

• *Gated clock*: the AND gate allows *Clock* pulses to pass into the *CLK* terminals only when the *Shift control* is active.

- Assume the binary content of *A* before the shift is 1011 and that of *B* is 0010.

- The serial transfer from A to B occurs in four steps.

| Timing Pulse  | Shif | t Re | gist | er A | Shift Register B |   |   |   |  |  |

|---------------|------|------|------|------|------------------|---|---|---|--|--|

| Initial value | 1    | 0    | 1    | 1    | 0                | 0 | 1 | 0 |  |  |

| After $T_1$   | 1    | 1    | 0    | 1    | 1                | 0 | 0 | 1 |  |  |

| After $T_2$   | 1    | 1    | 1    | 0    | 1                | 1 | 0 | 0 |  |  |

| After $T_3$   | 0    | 1    | 1    | 1    | 0                | 1 | 1 | 0 |  |  |

| After $T_4$   | 1    | 0    | 1    | 1    | 1                | 0 | 1 | 1 |  |  |

#### Serial-Transfer Example

## **Serial Adder**

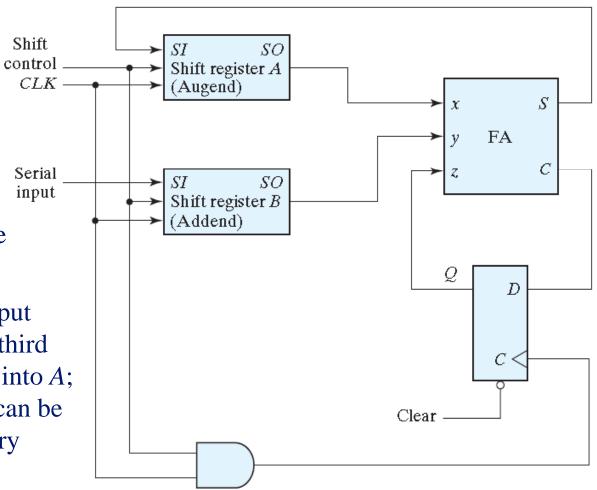

- Shift registers A and B store the two binary numbers to be added.

- A single full-adder (FA) adds one pair of bits at a time.

- The *D* FF temporarily stores the carry out for the next bit addition.

- The sum bit from the *S* output could be transferred into a third shift register or by shifting into *A*; while the serial input of *B* can be used to transfer a new binary number.

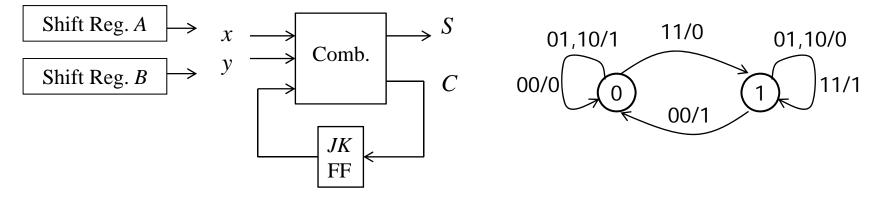

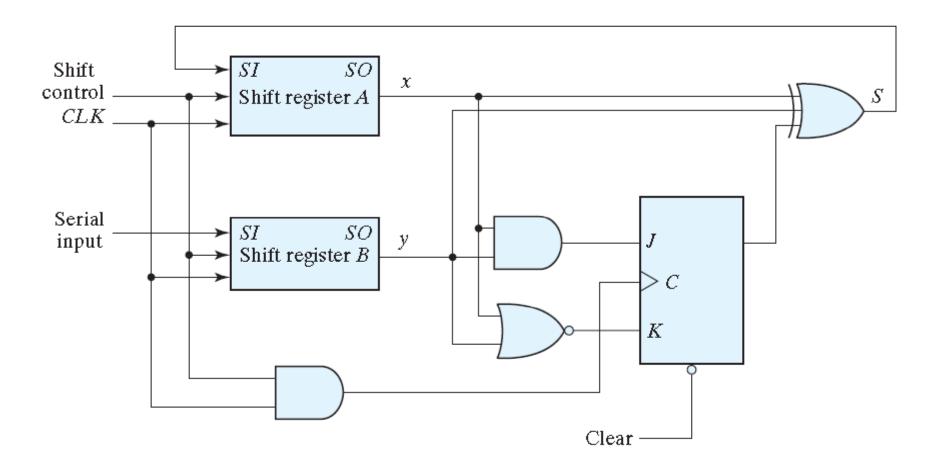

## **Redesign the Serial Adder with JK Flip-flops**

• The present state of Q is the present value of the carry.

| Present State | Inp | outs | Next State | Output | Flip-Flo | p Inputs | -           |                                       |                                          |                    |

|---------------|-----|------|------------|--------|----------|----------|-------------|---------------------------------------|------------------------------------------|--------------------|

| Q             | x   | y    | Q          | S      | Jq       | Kq       |             |                                       |                                          |                    |

| 0             | 0   | 0    | 0          | 0      | 0        | х        |             |                                       |                                          |                    |

| 0             | 0   | 1    | 0          | 1      | 0        | Х -      | 11/         | clin C                                |                                          |                    |

| 0             | 1   | 0    | 0          | 1      | 0        | X        | <i>ј</i> л. | Flip-F                                | -                                        |                    |

| 0             | 1   | 1    | 1          | 0      | 1        | Х -      | 1           | K                                     | Q(t +                                    |                    |

| 1             | 0   | 0    | 0          | 1      | Х        | 1        | 0<br>0      | $\begin{array}{c} 0 \\ 1 \end{array}$ | $\begin{array}{c} Q(t) \\ 0 \end{array}$ | No change<br>Reset |

| 1             | 0   | 1    | 1          | 0      | Х        | 0        | 1           | 0                                     | 1                                        | Set                |

| 1             | 1   | 0    | 1          | 0      | Х        | 0 -      | 1           | 1                                     | Q'(t)                                    | Complement         |

| 1             | 1   | 1    | 1          | 1      | Х        | 0        |             |                                       |                                          |                    |

| State | Table | for | <b>Serial</b> | Adder |

|-------|-------|-----|---------------|-------|

|       |       |     |               |       |

$$J_Q = xy,$$

$K_Q = x'y' = (x + y)',$   $S = x \oplus y \oplus Q$

$$J_Q = xy,$$

$K_Q = x'y' = (x + y)',$   $S = x \oplus y \oplus Q$

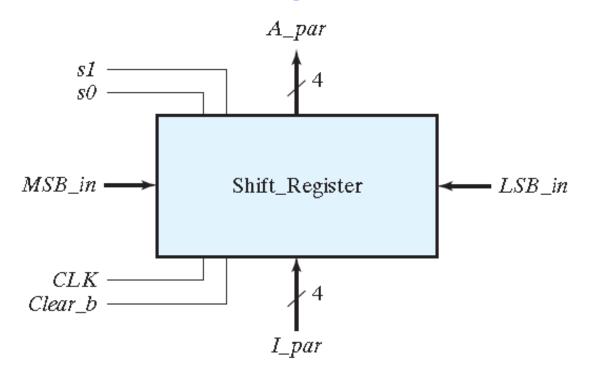

## **Universal Shift Register**

- The most general shift register has the following capabilities:

- 1. A *clear* control to clear the register to 0.

- 2. A *clock* input to synchronize the operations.

- 3. A *shift-right* control to enable the shift-right operation and the *serial* input and output lines associated with the shift right.

- 4. A *shift-left* control to enable the shift-left operation and the *serial* input and output lines associated with the shift left.

- 5. A *parallel-load* control to enable a parallel transfer and the *n parallel* input lines.

- 6. *n parallel outpu*t lines.

- 7. A control state that leaves the information in the register unchanged in response to the clock. Other shift registers may have only some of the preceding functions, with at least one shift operation.

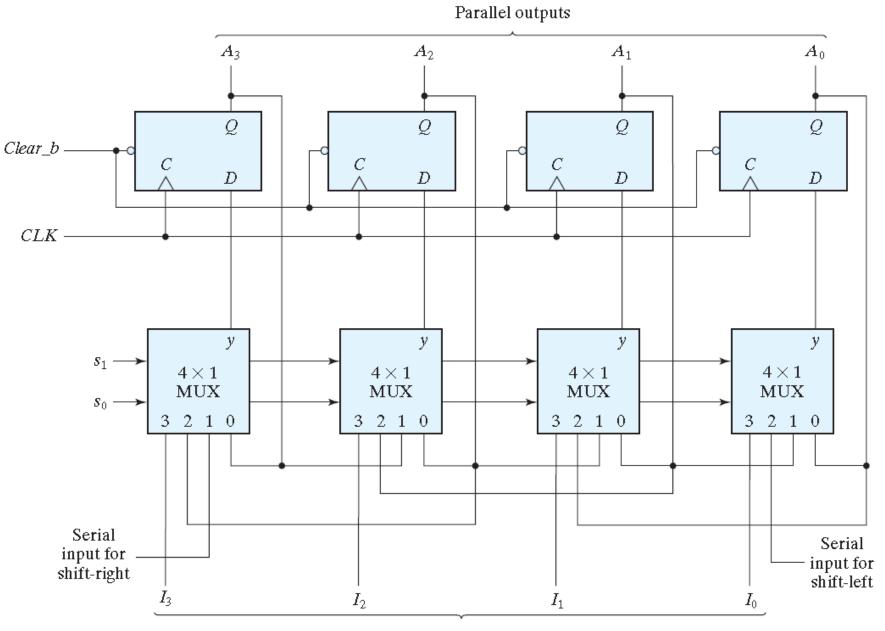

- A *universal shift register* can shift in both directions (*bidirectional shift*), and has both shifts and parallel-load capabilities.

## **4-bit Universal Shift Register**

Function Table for the Register of Fig. 6.7

| Mode       | Control         | _                         |

|------------|-----------------|---------------------------|

| <i>s</i> 1 | \$ <sub>0</sub> | <b>Register Operation</b> |

| 0          | 0               | No change                 |

| 0          | 1               | Shift right               |

| 1          | 0               | Shift left                |

| 1          | 1               | Parallel load             |

SISO: serial in serial outSIPO: serial in parallel outPIPO: parallel in serial outPISO: parallel in serial out

#### NCNU\_2013\_DD\_6\_12

Parallel inputs

# **6-3 Ripple Counters**

- Counter is a register that goes through a prescribed sequence of states upon the application of input pulses.

- A counter that follows the binary number sequence is called a *binary counter*.

- *n*-bit binary counter, consists of *n* FFs, can count in binary from 0 through  $2^n$  1.

- Counters have two categories: *ripple counters* and *synchronous counters*.

- Ripple counter: the *C* input of some or all FFs are triggered, not by the common clock pulses, but rather by the transition that occurs in other FF outputs.

- Synchronous counter: the *C* inputs of all FFs receive the common clock.

- Here, the binary and BCD ripple counters are introduced, and synchronous counters are presented in the next two sections.

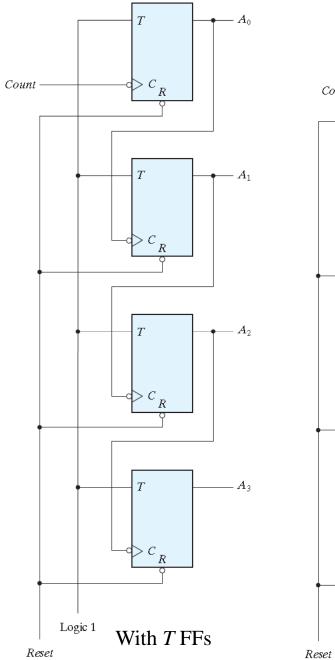

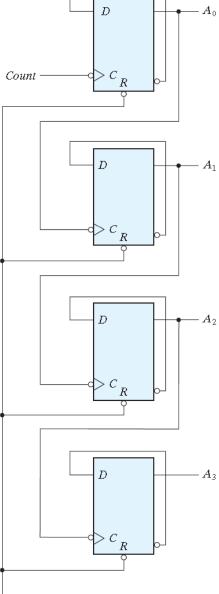

# **Binary Ripple Counter**

- A binary ripple counter consists of a series connection of complementing FFs, with the output of each FF connected to the *C* input of the next higher order FF.

- The FF holding the least significant bit receives the incoming count pulses.

- Complementing FF: (1) *JK* FF with the *J* and *K* inputs tied together, (2) *T* FF, (3) *D* FF with the complement output.

- Example: 4-bit binary ripple counter

- Binary count sequence: 4-bit

- Starts with binary 0 and increments by 1 with each count pulse input

- After the count of 15, the counter goes back to 0 to repeat the count.

| <b>A</b> <sub>3</sub> | A <sub>2</sub> | <b>A</b> <sub>1</sub> | <b>A</b> <sub>0</sub> |

|-----------------------|----------------|-----------------------|-----------------------|

| 0                     | 0              | 0                     | 0                     |

| 0                     | 0              | 0                     | 1                     |

| 0                     | 0              | 1                     | 0                     |

| 0                     | 0              | 1                     | 1                     |

| 0                     | 1              | 0                     | 0                     |

| 0                     | 1              | 0                     | 1                     |

| 0                     | 1              | 1                     | 0                     |

| 0                     | 1              | 1                     | 1                     |

| 1                     | 0              | 0                     | 0                     |

Table 6.4Binary Count Sequence

With *D* FFs

| Binary | Count Sequence |  |

|--------|----------------|--|

|--------|----------------|--|

| <b>A</b> <sub>3</sub> | <b>A</b> 2 | <b>A</b> 1 | Ao |

|-----------------------|------------|------------|----|

| 0                     | 0          | 0          | 0  |

| 0                     | 0          | 0          | 1  |

| 0                     | 0          | 1          | 0  |

| 0                     | 0          | 1          | 1  |

| 0                     | 1          | 0          | 0  |

| 0                     | 1          | 0          | 1  |

| 0                     | 1          | 1          | 0  |

| 0                     | 1          | 1          | 1  |

| 1                     | 0          | 0          | 0  |

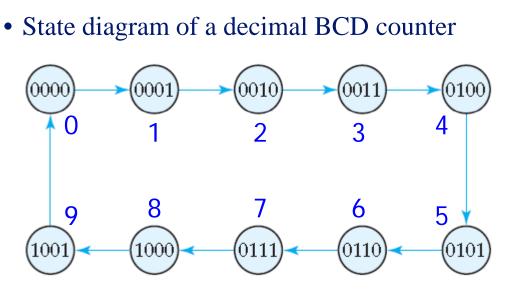

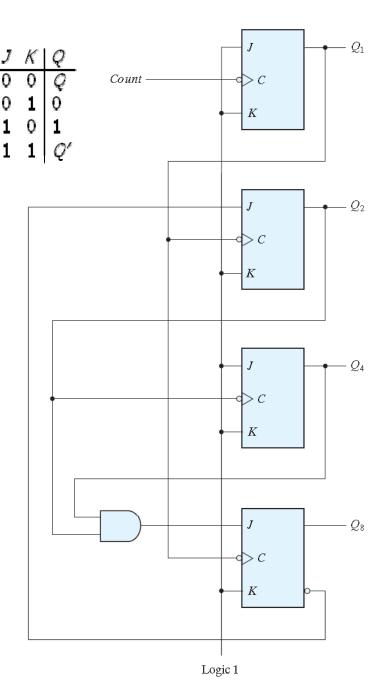

## **BCD Ripple Counter**

$Q_1$ : changes state after each clock pulse.

- $Q_2$ : complements every time  $Q_1$  goes from 1 to 0, as long as  $Q_8 = 0$ . When  $Q_8$  becomes 1,  $Q_2$ remains at 0.

- $Q_4$ : complements every time  $Q_2$  goes from 1 to 0.

- $Q_8$ : remains at 0 as long as  $Q_2$  or  $Q_4$  is 0. When both  $Q_2$  and  $Q_4$  become 1,  $Q_8$  complements when  $Q_1$ goes from 1 to 0.  $Q_8$  is cleared on the next transition of  $Q_1$ .

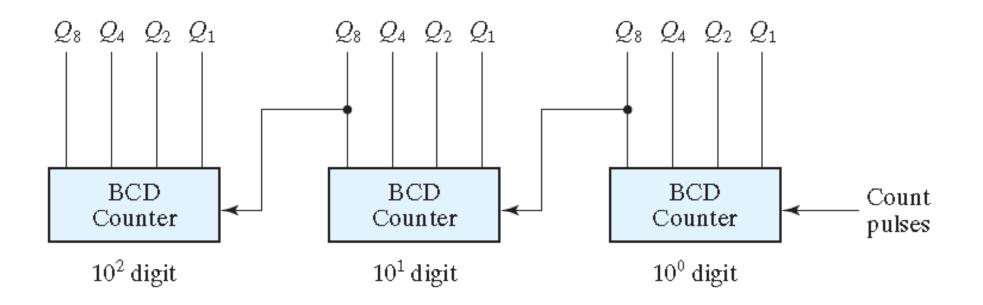

#### **Three-decade BCD Counter**

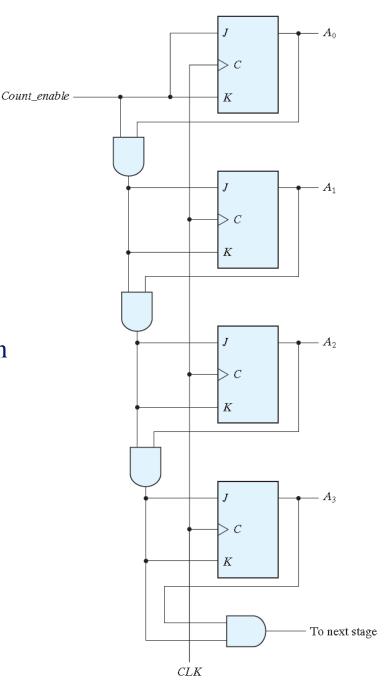

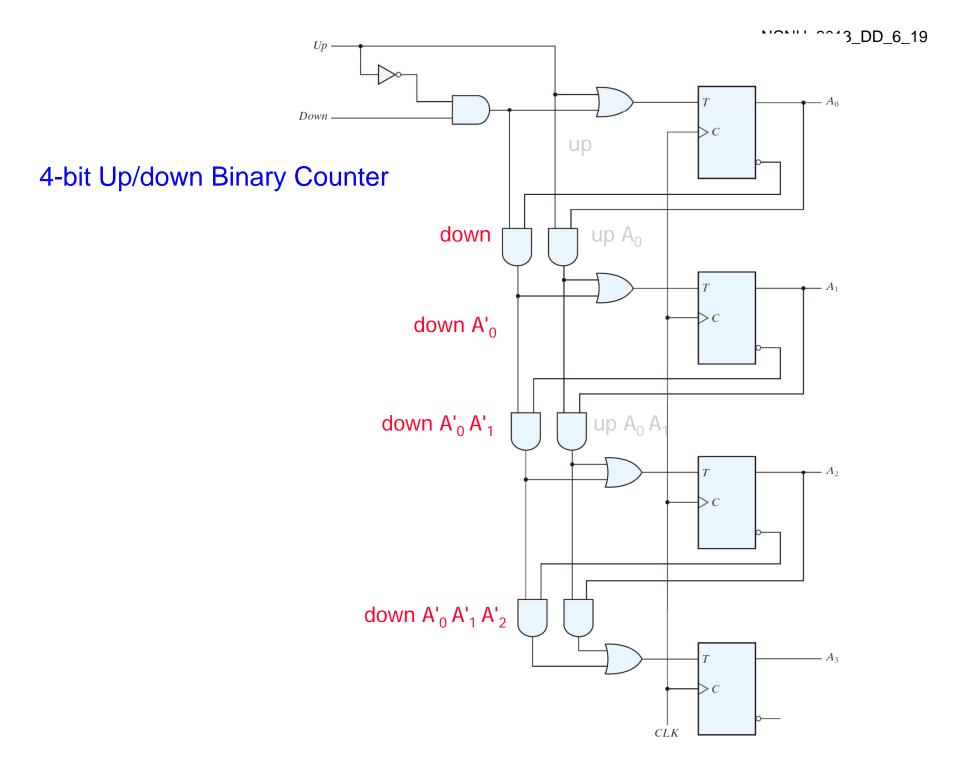

## **6-4 Synchronous Counters**

- A common clock triggers all FFs simultaneously.

- If T = 0 or J = K = 0, the FF does not change state.

- If T = 1 or J = K = 1, the FF complements.

#### **Binary Counter**

- The FF in the least significant position is complemented with every pulse, and the FF in any other position is complemented when all the bits in the lower significant positions are equal to 1.

- Synchronous binary counters have a regular pattern and can be constructed with complementing FFs and gates.

## **BCD Counters**

State Table for BCD Counter

| Р          | resent     | t State        | 5                     |            | Next State |                       |            | Output | Fl              | ip-Flo          | թ Iոթւ          | ıts             |

|------------|------------|----------------|-----------------------|------------|------------|-----------------------|------------|--------|-----------------|-----------------|-----------------|-----------------|

| <b>Q</b> 8 | <b>Q</b> 4 | Q <sub>2</sub> | <b>Q</b> <sub>1</sub> | <b>Q</b> 8 | <b>Q</b> 4 | <b>Q</b> <sub>2</sub> | <b>Q</b> 1 | y y    | TQ <sub>8</sub> | TQ <sub>4</sub> | TQ <sub>2</sub> | TQ <sub>1</sub> |

| 0          | 0          | 0              | 0                     | 0          | 0          | 0                     | 1          | 0      | 0               | 0               | 0               | 1               |

| 0          | 0          | 0              | 1                     | 0          | 0          | 1                     | 0          | 0      | 0               | 0               | 1               | 1               |

| 0          | 0          | 1              | 0                     | 0          | 0          | 1                     | 1          | 0      | 0               | 0               | 0               | 1               |

| 0          | 0          | 1              | 1                     | 0          | 1          | 0                     | 0          | 0      | 0               | 1               | 1               | 1               |

| 0          | 1          | 0              | 0                     | 0          | 1          | 0                     | 1          | 0      | 0               | 0               | 0               | 1               |

| 0          | 1          | 0              | 1                     | 0          | 1          | 1                     | 0          | 0      | 0               | 0               | 1               | 1               |

| 0          | 1          | 1              | 0                     | 0          | 1          | 1                     | 1          | 0      | 0               | 0               | 0               | 1               |

| 0          | 1          | 1              | 1                     | 1          | 0          | 0                     | 0          | 0      | 1               | 1               | 1               | 1               |

| 1          | 0          | 0              | 0                     | 1          | 0          | 0                     | 1          | 0      | 0               | 0               | 0               | 1               |

| 1          | 0          | 0              | 1                     | 0          | 0          | 0                     | 0          | 1      | 1               | 0               | 0               | 1               |

- The FF input equations can be simplified by means of maps.

- The unused states for minterms 10 to 15 are taken as don't-care terms.

- The simplified functions are

$T_{Q1} = 1, \quad T_{Q2} = Q'_{8}Q_{1}, \quad T_{Q4} = Q_{2}Q_{1}, \quad T_{Q8} = Q_{8}Q_{1} + Q_{4}Q_{2}Q_{1}$  $y = Q_{8}Q_{1}$

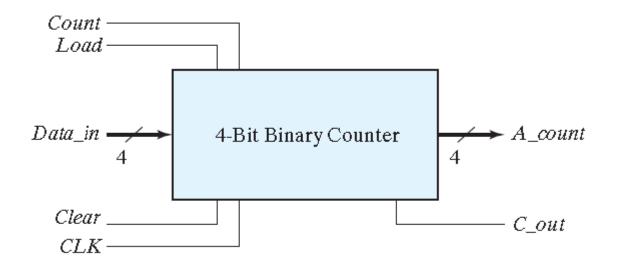

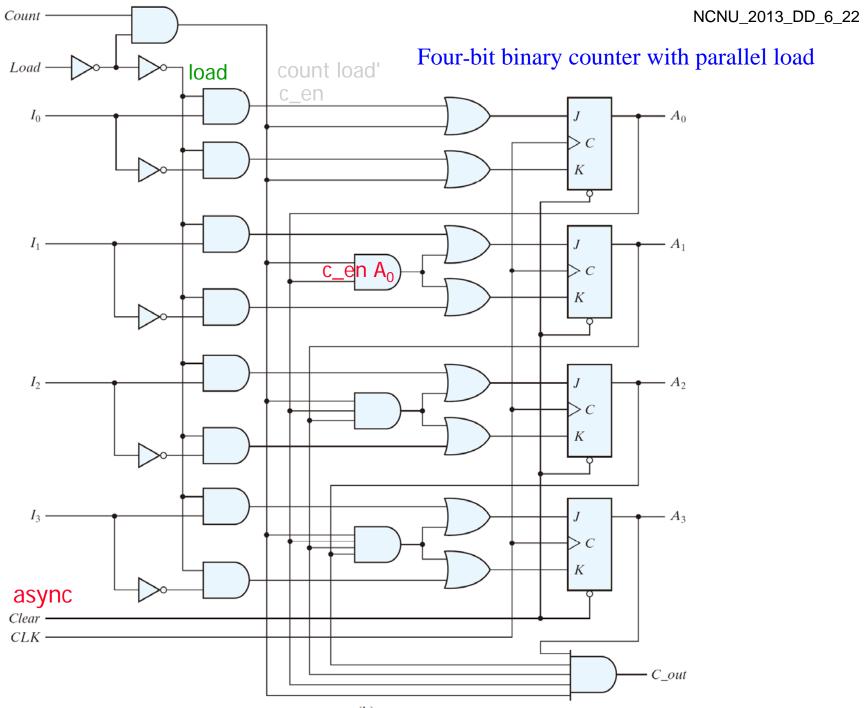

## **Binary Counter with Parallel Load**

Function Table for the Counter of Fig. 6.14

| Clear | CLK | Load | Count | Function                |

|-------|-----|------|-------|-------------------------|

| 0     | Х   | Х    | Х     | Clear to 0              |

| 1     | 1   | 1    | Х     | Load inputs             |

| 1     | 1   | 0    | 1     | Count next binary state |

| 1     | Î   | 0    | 0     | No change               |

(b)

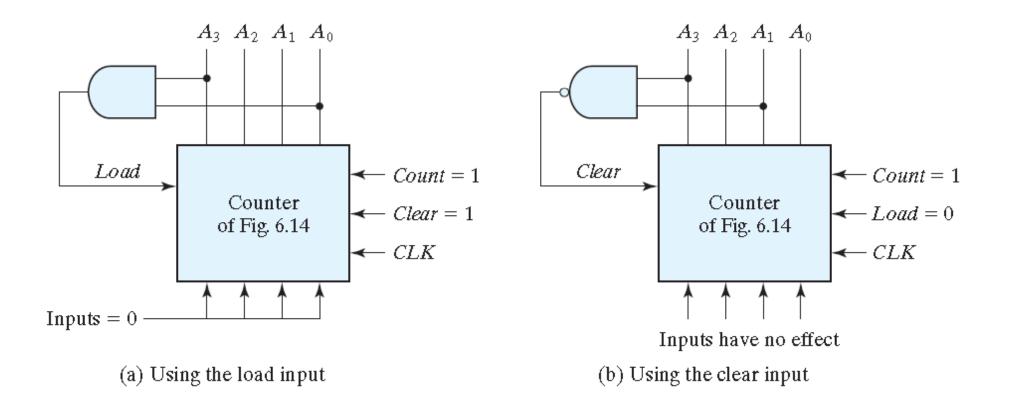

- A counter with a parallel load can be used to generate any desired count sequence.

- Two ways to achieve a BCD counter using a counter with parallel load.

## **6-5 Other Counters**

- Counters can be designed to generate any desired sequence of states.

- A divide-by-*N* counter (a.k.a. a modulo-*N* counter) is a counter that goes through a repeated sequence of *N* states; and the sequence may follow the binary count or any other arbitrary sequence.

- A few examples of non-binary counters are presented here.

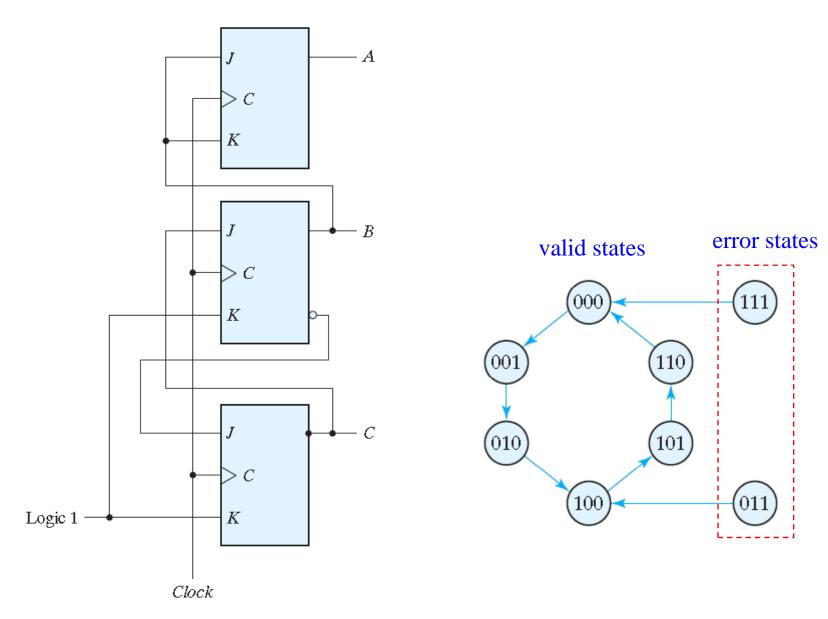

#### **Counter with Unused States**

- *n* FFs has  $2^n$  binary states, while state table may have unused state.

- The unused states may be treated as don't-care or assigned specific next states.

- Once the circuit is designed and constructed, outside interference may cause the circuit to enter one of the unused states.

- Ensure that the circuit eventually goes into one of the valid states so that it can resume normal operation; and avoid the sequential circuit circulates among unused states.

- If the unused states are treated as don't-care conditions, then once the circuit is designed, it must be investigated to determine the effect of the unused states.

- The next state from an unused state can be determined from the circuit designed.

| Pres | sent S | itate | Next State |   |   | Flip-Flop Inputs |                |                |                |    |    |  |

|------|--------|-------|------------|---|---|------------------|----------------|----------------|----------------|----|----|--|

| A    | B      | С     | A          | B | С | J <sub>A</sub>   | K <sub>A</sub> | J <sub>B</sub> | K <sub>B</sub> | Jc | Kc |  |

| 0    | 0      | 0     | 0          | 0 | 1 | 0                | Х              | 0              | Х              | 1  | Х  |  |

| 0    | 0      | 1     | 0          | 1 | 0 | 0                | Х              | 1              | Х              | Х  | 1  |  |

| 0    | 1      | 0     | 1          | 0 | 0 | 1                | Х              | Х              | 1              | 0  | Х  |  |

| 1    | 0      | 0     | 1          | 0 | 1 | Х                | 0              | 0              | Х              | 1  | Х  |  |

| 1    | 0      | 1     | 1          | 1 | 0 | Х                | 0              | 1              | Х              | Х  | 1  |  |

| 1    | 1      | 0     | 0          | 0 | 0 | Х                | 1              | Х              | 1              | 0  | Х  |  |

#### State Table for Counter

- Six repeated sequence of states, with FFs *B* and *C* repeating the binary count 00, 01, 10, and FF *A* alternating between 0 and 1 every three counts.

- The sequence of the counter is not straight binary, and two states, 011 and 111, are not included in the count.

- The choice of *JK* FFs results in the FF input conditions listed in the table. Inputs  $K_B$  and  $K_C$  have only 1's and X's in their columns, so these inputs are always equal to 1.

- The other FF input equations can be simplified by using minterms 3 and 7 as don't-care conditions. The simplified equations are

$J_A = B$   $K_A = B$ ,  $J_B = C$   $K_B = 1$ ,  $J_C = B'$   $K_C = 1$

## **Self-correcting Counter**

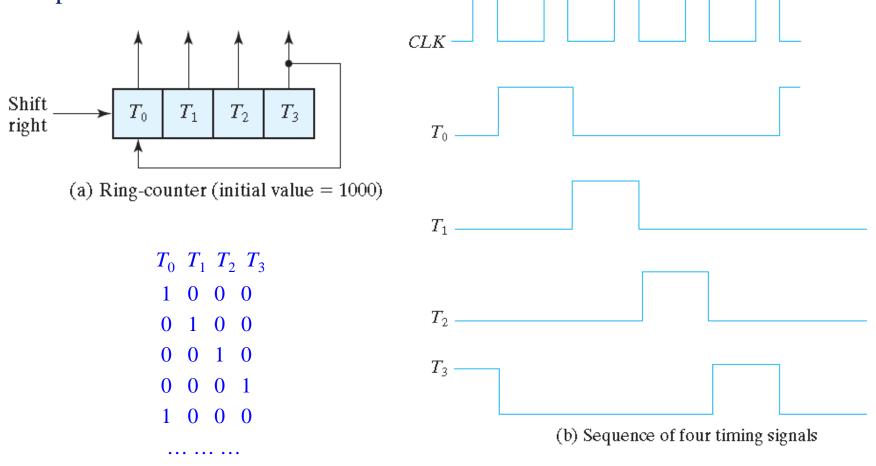

# **Ring Counter**

- Ring counter: a circular shift register with only one FF being set at any particular time; all others are cleared.

- The single bit is shifted from one FF to the next.

- Example:

## **Generation of Timing Signals**

- Application of counters

- Counters may be used to generate timing signals to control the sequence of operations in a digital system.

- Approaches for generation of 2<sup>*n*</sup> timing signals

- 1. a shift register with  $2^n$  FFs

- 2. an *n*-bit binary counter together with an *n*-to- $2^n$ -line decoder

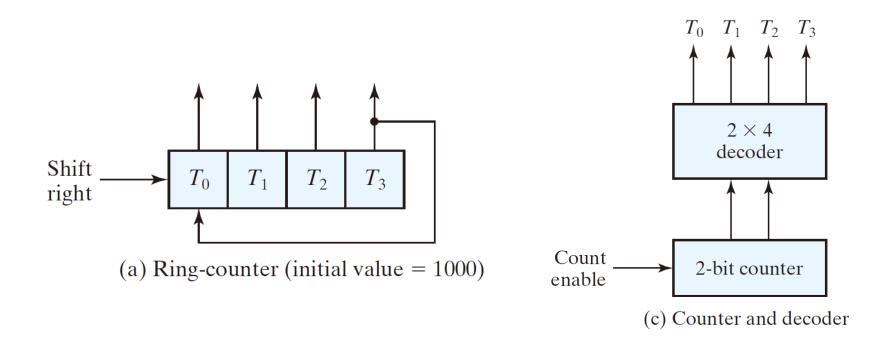

# **Johnson Counter**

- A *k*-bit ring counter circulates a single bit among the FFs to provide *k* distinguishable states.

- The number of states is doubled for a *switch-tail* ring counter.

- A switch-tail ring counter is a circular shift register with the complemented output of the last FF connected to the input of the first FF.

- In general, a *k*-bit switch-tail ring counter will go through a sequence of 2*k* states.

- Starting from all 0's, each shift operation inserts 1's from the left until the register is filled with all 1's.

- In the next sequences, 0's are inserted from the left until the register is again filled with all 0's.

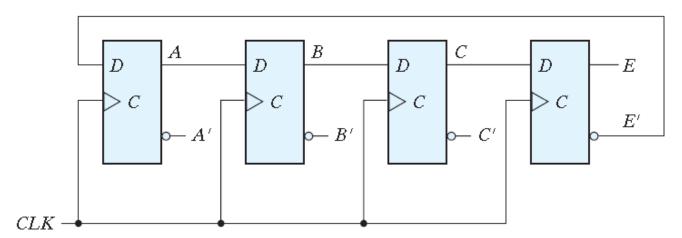

## **Construction of a Johnson Counter**

- 2k decoding gates are needed to provide outputs for 2 k timing signals.

- The decoding gates are the eight AND gates listed in the table.

- Since each gate is enabled during one particular state sequence, the outputs of the gates generate eight timing signals in succession.

| Sequence           | Fli            | p-flop | outpu | uts | AND gate required |

|--------------------|----------------|--------|-------|-----|-------------------|

| Sequence<br>number | $\overline{A}$ | В      | С     | E   | for output        |

| 1                  | 0              | 0      | 0     | 0   | A'E'              |

| 2                  | 1              | 0      | 0     | 0   | AB'               |

| 3                  | 1              | 1      | 0     | 0   | BC'               |

| 4                  | 1              | 1      | 1     | 0   | CE'               |

| 5                  | 1              | 1      | 1     | 1   | AE                |

| 6                  | 0              | 1      | 1     | 1   | A'B               |

| 7                  | 0              | 0      | 1     | 1   | B'C               |

| 8                  | 0              | 0      | 0     | 1   | C'E               |